3D芯片堆叠技术成功突破四层!

既然工艺技术提升受阻,或者要换个方式来提高未来芯片的性能了,也许3D堆叠技术是一种选择。据Tom’s Hardware报道,新加坡科技研究局(A*STAR)旗下微电子研究院Institute of Microeletronics(IME)的研究人员刚刚实现了一项技术突破,实现了多达四个半导体层的堆叠。与传统的二维制造技术相比,可以节省50%的成本,该技术可能会用于未来的CPU和GPU上,或许真正的新一代3D芯片堆叠就在眼前。

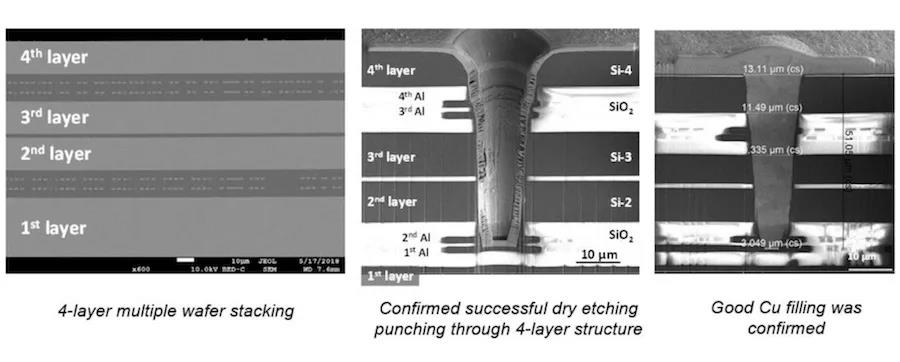

相比此前台积电和AMD的SRAM堆叠技术,IME的这项新技术更进一步。在AMD展示采用3D堆叠技术的Ryzen9 5900X处理器的原型设计里,基于台积电无损芯片堆叠技术的产品只有两层,第一层是Zen 3架构的CCX,第二层是96MB的SRAM缓存。IME的研究人员则展示了另外一种工艺,通过TSV(硅通孔技术)成功键合(wafer bonding)了四个独立的硅层,允许不同模具之间通信。

具体做法是第一层半导体层的面朝第二层,第二层也面向第一层。第二层半导体层的背则朝第三层的背,第三层的面又朝向第四层的面。半导体层结合后,IME 透过专门设计路径蚀刻“压紧”,最终藉 TSV 整合使电流数据流过。

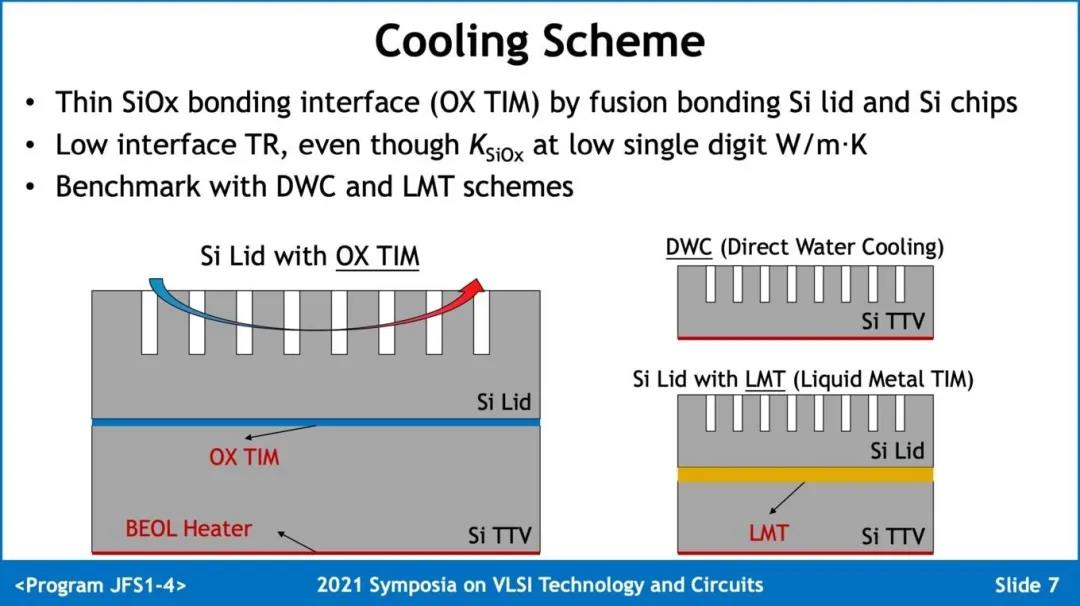

这样的技术带来的好处是显而易见的,可以允许芯片由不同工艺的组件在不同晶圆中制造,在近期英特尔的演讲中可以感觉到,新芯片的设计上已经往这方面的思路发展了。这样的堆叠当然也会带来其他的问题,就如许多人所想的那样,虽然芯片效率提高了,但要面对散热问题,所以会看到许多奇特的、直接用在芯片上的散热技术开始浮现。

就如《电子工程专辑》日前报道的,一种在芯片中直接蚀刻出水道的“片上水冷”散热方式。

利用融合/混合键合技术实现两层以上多层W2W堆栈的能力对于下一代产品至关重要。这包括各种应用,例如行动运算、高性能运算和绘图运算,都需要具有成本效益的3D整合技术。

3D整合、TSV制程和多晶圆熔接技术的突破,将使组件制造商能够更有效地整合具有高附加价值的3D产品。对于设备制造商、设备供货商和材料供货商而言,这一发展将意味着具有更低成本3D DRAM和制造的新商机。

文章来源:国际电子商情,如有侵权,请联系我们删除

以上即是本站关于 《3D芯片堆叠技术成功突破四层!》 全部内容,多谢阅览!

相关新闻

深圳市时时发控股有限公司专营电子元件批发、电子元件采购,是综合性的电子元器件网上商城。

电子元器件商城主营:存储IC/内存条/SSD/HDD/CPU/GPU等,品牌包括:三星,镁光,海力士,英特尔,英伟达等。

© 2022 深圳市时时发控股有限公司 粤ICP备19078955号

网站地图

扫描二维码添加客服微信获取报价

MTA32ATF4G64HZ-2G6B2 SODIMM DDR4 镁光

MTA32ATF4G64HZ-2G6B2 SODIMM DDR4 镁光